# JTAG テストによる基板検査

## コスト削減と品質向上に役立つ10のヒント(前編)

アンドールシステムサポート(株)/谷口 正純、佐々木 陽助

### 1. はじめに

海外メーカーとの競合が激しいエレクトロニクス業界では、製品検査のスピードと効率化が利益と開発サイクルの 短縮に重大な影響を与える。

今回紹介する『JTAGテスト』は、IEEE1149.1バウンダリスキャンの技術を使ったテスト手法であり、最近増えているBGAパッケージの部品(DDRメモリ、FPGA、マイコン、DSPなど)のはんだ不良によるトラブルを検査する最善の方法である。

現在、企業で使用しているインサーキットテスタ、ファンクションテスタに、業界スタンダードである JTAG Technologies社のJTAGテストツール『JTAG ProVision』を組み込む方法と有効活用するためのヒントを紹介する。

下記のチェックリストに一つでもあてはまる方は、JTAGテスト手法の導入を検討する良い機会となる。JTAGテストを実施して、開発現場、生産現場にフィードバックすることにより、はんだ不良・パターン不良を改善できる。

### JTAGテストによる基板検査の 改善

- 1.7つのチェックリスト

- □故障箇所が分からず、BGAを手あた り次第に交換・リワークしている

- □検査装置を導入したが、BGA基板の 検査に十分な効果がなかった

- □テストカバレッジを改善したいが、検 査コストが負担になっている

- □故障解析できない不良基板があり、基

### 板を廃棄している

- □検査とフラッシュメモリの書き込みを別工程で実施している

- □DDRメモリのはんだ不良箇所が分からない

- □新製品に対して開発期間の短縮の要求が強い

### 2.ヒント① あらゆる部門で直接的な利益を得られる JTAGテスト

競合に打ち勝ちプロダクトを成功させるためには、将来を見据えて、製品の開発・製造・検査・故障解析のサイクルを 改善できる検査手法を選択することが重要である。正しい 基板検査の手法を選択することにより、企業内の設計部門、 生産・製造部門、品質管理部門、メンテナンス部門などすべ

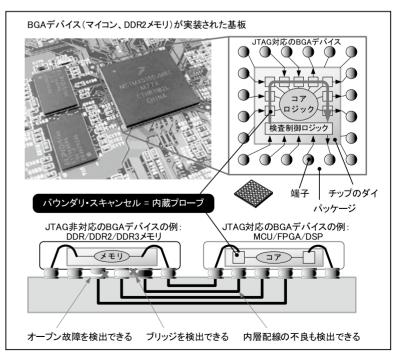

図1 プロービングできないBGA基板とJTAGテストの基礎

ての部門が恩恵を受けることができる。

全部門が共通で使用できる検査装置には、テストの容易性とテストカバレッジの改善、持ち運びの容易性が求められる。製品基板に実装されている主要部品であるマイコン、FPGA、PLD、DSP、プロセッサ、チップセットは、すでにJTAGテストを実施するためのバウンダリスキャンのロジックが内蔵されているため、図1のように、ほとんどの被検査基板はJTAGテストを適用できる環境が整っているといえる。

### ●国際規格の基板検査手法 JTAGテスト

このテストの仕組みは、1990年に現在のBGA基板を検査する目的として、IEEE1149.1としてJTAGテスト(バウンダリスキャン方式)が国際的に規格化された。JTAGテストでは基板上の主要部品をPCから制御して、通電試験・オンボードプログラミングを実施できる。特別に複雑な回路は必要なく、JTAGの4本の信号(もしくは5本の信号)のみで基板全体を検査できる容易性と広いテストカバレッジが特徴である。JTAGテストは、製品基板上のデバ

イス内部のバウンダリ・スキャンセルをプローブとして使うテスト手法であり、物理的なプロービングができないBGA部品も検査できる。

JTAGテストは、製品のプロトタイプ 段階から基板検査を実施する環境が整う ため、設計者にとっては基板のデバッグ期 間の短縮と故障解析の負担を低減できる。 また、製造・検査の現場では、検査設備のコ ストの削減と検査時間の短縮、さらに製品 の品質を向上できる。

以降の章に、生産現場と開発現場で起きている基板検査の問題点と改善策を検討するためのヒントを紹介する。

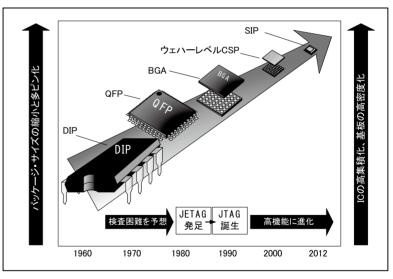

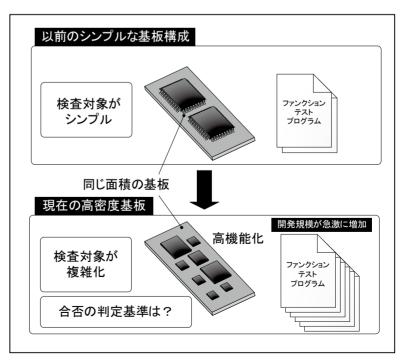

# 3.ヒント② IC パッケージの遍歴と検査容易化設計 DFT

ICパッケージは、図2のとおり、高密度 化とピン数の増加が進んでいる。1980 年代のエレクトロニクス業界では、現在 の企業が抱えている検査の問題を予測し、 JETAG (Joint European Test Action Group) という団体が発足した。1990 年には多くの企業が賛同して、JTAGテス ト(バウンダリスキャン方式)を『IEEEStd1149.1 TAP and Boundary-Scan Architecture』として標準化した。エレクトロニクス業界による強力なテスト技術の標準化には、他のテスト手法の多くの欠点を克服する目的があった。

### ●重要となったテスト容易化設計 DFT

ICの発展により、テスト容易化設計DFT (Design For Test)は、製品を検査する段階におけるターゲット機能の制御性と観測性を向上するために重要性が増してきている。当初、検証は設計を検証するためのデバッグと製造上の不具合の検出を混同していた。設計の複雑さが増しても、それらを分離して取り組めばこれらのタスクはより扱いやすくなる。必要なことは設計のデバッグより前に、プロトタイプの製造不良を検出してクリアする方法である。製品の複雑さが増すので、量産時の早期段階で不具合を検出して修理することが重要となる。そのため、多くの工場ではいくつかのステップに分けて、複数のテスト手法を使用している。

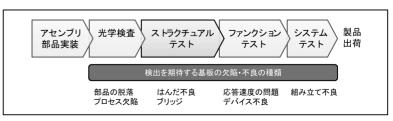

多くのテスト手法は、一般的に図3に示される製造工程

図2 ICの高集積化とJTAGテストの誕生

図3 製造現場における検査フローと検出できる欠陥と不良

となる。製造工程の中で、アセンブリと光学検査の後、インサーキットテストなどのストラクチュアルテストがファンクションテストの前に実行される。ストラクチュアルテストでは、はんだのオープン、ブリッジ、異部品の実装などを検出でき、一般的にストラクチュアルテストは迅速に準備できる。また、自動化されたソフトウェアにより、検出された不具合は基板上にテストポイントが十分にあれば、非常に迅速に故障診断ができる。

### 4.ヒント③ インサーキットテストが抱える課題

長年にわたり広く使用されてきたストラクチュアルテスト手法は、インサーキットテストであり、ファンクションテストの制限を補足するために開発された。インサーキットテストでは電気的信号が被検査基板にドライブされ、その結果がピン治具のプローブにより読み取られる。それぞれの部品に対して、製造上の不具合を検出するためのテストベクタを用意することにより、部品レベルの故障診断が可能となる。このテスト手法は、DIPパッケージ部品とスルーホールがある非検査基板に対して非常に適していた。

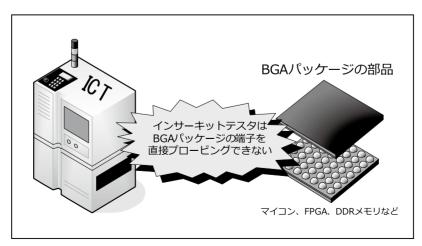

### ●BGAパッケージに対応できない

現在の生産ラインでは、狭ピッチでピン数が多い部品 (QFP、CSP、FCAなど)が増え、テストアクセスは厳しく制限されるようになり、図4のようにBGAパッケージでは部品実装後にはプロービングできないため、テストに対応できない基板が増えている。

### ●非検査基板の信頼性低下とテストの信頼性

インサーキットテスト手法では、最初にピン冶具が内部

の回路ノードに対して機械的にロジカルにアクセスする。 このロジックの侵入はバックドライブと呼ばれるが、この 使用方法はデバイス固有の仕様を外れるため、被検査基板 の品質、信頼性において悪影響を及ぼす可能性がある。

インサーキットテストで使用するピン治具は、プローブの接触が完全ではないなどデメリットがある。現在はボードサイズがシュリンクされ、治具のピンが弱くなり、テスト結果が信頼性に欠け、直接量産コストに響いてしまう。特に工場が治具において、フラックスのビルドアップが発生する可能性のあるクリーンでないプロセスを採用している時は、信頼性の低下が著しい(表 1)。

### ●インサーキットテストの優位性と将来性

インサーキットテストのメリットであるテスト開発のスピードと故障診断機能により、ファンクションを実施する前にできるだけ多くの不具合を見つけることが望まれる。しかし、ストラクチュアルテストで不具合の原因を迅速に判断するためには、基板上に十分なテストポイントが必要となる。現在のように基板設計と部品実装の複雑さが増し、高いレベルの検査カバレッジを達成するために、新しいストラクチュアルテストを検討している企業が多くみられる。

インサーキットテスタは、5,000ノード以上の能力をもつテスタでテスト範囲を補っている企業もあるが、ピン冶具はますます高価になり、高密度化が進む中で信頼性の問題も出ている。生産現場ではインサーキットテストの優位性があるにもかかわらず、基板の生産技術者はテストカバレッジが年々減少していることを実感している。

図4 インサーキットテストとBGAパッケージ部品のテスト

### 5.ヒント④ ファンクションテストが抱える課題

ファンクションテストは、各企業、各製品ごと作る独自の テスト手法である。エレクトロニクス産業の初期の時代では、多くのシステムは単純な構成で部品点数も少なかった。 そのため、テストプログラムを簡単に短期間で開発でき、システムの機能テストを実施することができた。

### ●検査範囲、合否判定が設計者に依存する

今日でも多くの企業では、このようなシステム全体の ファンクションテストを実施している。しかし、現在では

システムが複雑になり、ファンクションテストの開発には長期間を必要とする。テストプログラムによる故障解析は、設計者に依存する独自のテスト手法であるため、検査範囲や合否判定基準は設計者に依存する部分が多く残る。また、ファンクションテストでは、故障診断が非常に難しく、故障している部品やピン番号を特定するには、設計者の情報と技術スキルが必要となる。

このような理由により、簡易的なファンクションテストを基板レベルで実施するケースがある。検査範囲の細分化によって、テスト準備と故障診断を実行しやすくなる。しかし、今日の急激なICの集積度増加により、基板レベルのファンクションテストにおいても、システムレベルで遭遇する課題に直面している(図5)。

### ●システムスピードや特殊なシーケンス 下で発生する不良を検出できる

製造ラインにおいて、ファンクションテストは、ストラクチュアルテストの次のステップとして実施され、動作上の問題点(システムスピードや特殊なシーケンスの下でのみ発生する問題点)の不良を検出することを目的としている。ファンクションテストの特徴として、設計変更に対して対応できないことである。小さな設計変更でさえ、苦労して開発したテストプログラムが無駄になってしまう。その上、ファンクションテストでは、製造上の不具合に対して故障箇所を明確に特定できないた

め、フォルトカバレッジが低い可能性がある。

ファンクションテストプログラムと故障診断は、一般的には製品の設計者が用意することになる。しかし、多くの企業では設計者のリソースが不足しており、詳細なピンレベルにまで落とした故障解析は不可能であることが多い。その結果、設計者は製品のプログラムの設計、テストプログラムの設計を行い、さらに設計者が自ら故障解析を行う状況になっている。また、製品の検査が未知の部分が残ってしまうため、製品の品質と信頼性を引き下げることになってしまう。

# インサーキットテストの特徴 【テスト準備】 ・基板上にテストパッドが必要 ・基板の種類毎にピン治具が必要 「アストスピード】 ・高速にテスト結果がわかる インサーキットテストが抱える誤題 【非検査基板】 ・バックドライブにより品質が低下 ・テストパッドによるノイズ耐性悪化 ・ピン接触の信頼性が低い

表1 インサーキットテストの特徴と課題

図5 基板の高密度化により複雑化するファンクションテスト

もし、修理期日が決まっている製品であれば、故障解析・ デバッグする時間が取れないまま、結果としては故障基板 を積み上げることになる。多くの場合、最後には基板が廃 棄されて、その問題は未解決のままになり、製造へのフィー ドバックができないことになる(表2)。

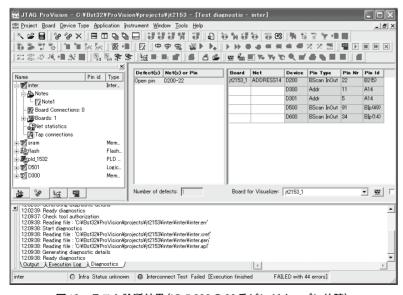

### 6.ヒント⑤ 課題を解決するJTAGテストの基本と応用

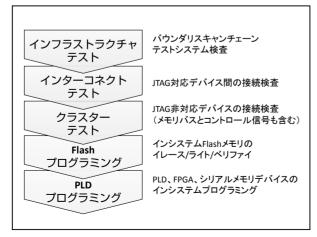

JTAGテストは、図6のように、4本(もしくは5本)の信号で基板全体をテストすることができる。JTAGテストでは、いくつかのテストを組み合わせて、テスト範囲を補完してテストカバレッジを向上している。JTAGテストでは、マイコンのプログラムやFPGAのロジックは不要であり、部品内部のバウンダリ・スキャンセルと呼ばれるシフトレジスタをPCから制御してテストを行う。

JTAGテスト用のテストプログラムは、JTAGテストツール『JTAG ProVision』により自動生成される。したがって、

検査カバレッジと合否判定はJTAGテストツールで自動化され、さらに故障診断まで自動化でき瞬時に基板上の故障 箇所が分かる。

### ●インフラストラクチャテスト

基板レベルの検査であるJTAGテストは、図7のような基板の外部に接続されたJTAGコントローラから実行する。JTAGテストでは、必ずインフラストラクチャテストをテストシーケンスの最初に実行する。インフラストラクチャテストでは、JTAG対応デバイスが正しい型番、リビジョンの部品であるか、JTAG信号の断線、ショート、ハンダ不良などの不良を検出できる。

JTAGテスト時に、JTAG対応デバイスのピンから信号の入出力を行う正しく制御できるか判断するための重要なテストである。テスト方法は、JTAG対応のデバイスのIDコード、レジスタを読み込み、期待値と比較して合否判定を

行うため、テスト設計者に依存しないテ スト手法である。

### ファンクションテストの特徴

### 【テスト準備】

- ・設計者によるプログラム開発

- ・複雑なシーケンスの検査ができる

### 【故障解析】

- ・機能レベルでの診断結果

- ・故障解析・分析の仕様書が必要

### ファンクションテストが抱える課題

### 【非検査基板】

- ・反復修理による基板の品質低下

- ・基板を廃棄する可能性が高い

### 【テストの課題】

- ・詳細故障診断ができない

- ・故障基板を廃棄する可能性が高い

### 表2 ファンクションテストの特徴と課題

# - わずか 4 本の JTAG 信号で基板全体を検査 - プルアップ / ブルタップ / ブルアップ / ブルタップ / ブルアップ / ブルタップ /

図6 基板全体を検査できるJTAGテスト

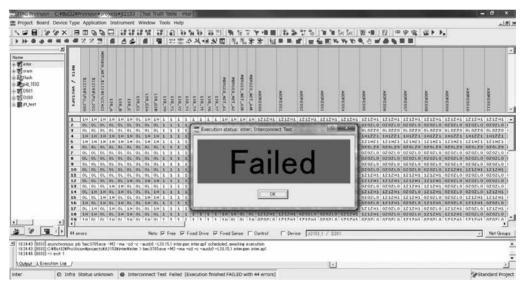

### ●インターコネクトテスト

インターコネクトテストは、被検査基板上のすべてのJTAG対応デバイス間のパターン、はんだ不良を検査できる。『JTAG ProVision』で自動生成されたテストプログラムにより、PCに接続したJTAGコントローラを介して、基板上のJTAG対応デバイスのピンがプローブの代わりとして制御される。インターコネ

図7 プロトタイプ段階でも使用できる コンパクトな JTAG テストツール

クトテストでは、デバイスのピンを信号出力、信号入力、ハイインピーダンスを自動的に切り替えながらテストを実行して、パターン不良・はんだ不良箇所をピンレベルで特定できる。

合否判定と故障解析結果は、図8のように表示されるため、作業員が合否判断をすることはなく、また、JTAGテストの特徴として部品内部のボンディングワイヤ、デバイスのピン、はんだ接合部、基板内のパターンを電気的にテストするため、物理的なピン治具を使ったテストよりも広範囲で検査している。信頼性が求められる製品の製造現場で、多く採用されている理由である。

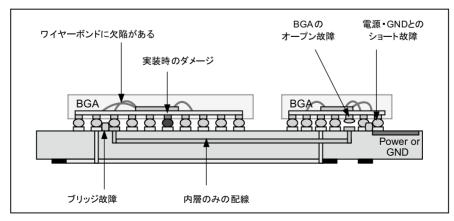

### ●クラスタテスト

被検査基板上には、JTAGテスト対応デバイスと非対応

デバイスが混在している。そのようなボードにおいて高い 検査カバレッジを実現するためには、JTAGテスト対応デ バイス間のインターコネクトテスト以外にも検査範囲を広 げることが重要である。

業界スタンダードの『JTAG ProVision』では、JTAG非対応デバイスの部品ライブラリが10万種類以上提供される。この部品ライブラリには、部品ごとの入出力ピン、電源ピン、GNDピンなどのピン属性とロジックの真理値表が含まれている。クラスタテストでは、この部品ライブラリを使ってテストプログラムと合否判定基準が自動生成される。JTAG対応デバイスから実際に周辺の回路を動作させてテストを行うため、図9のように基板上のはんだ不良、はんだブリッジ、部品未実装、JTAG非対応部品のボンディングワイヤ不良など、典型的な製造不良に対するテストを容

図8 『JTAG ProVision』による基板テストの結果

図9 BGA基板に潜む故障の可能性

易に実行できる。

このようにJTAGテストでは、JTAGテスト対応デバイスが基板上に1つしか実装されない場合でも、十分に検査カバレッジを得ることができる。

### ●メモリクラスタテスト

最近特にトラブルが多い部品は、DDRメモリである。 JEDECによりパッケージの標準がBGAとなり、高速信号であることから基板の内層のみでパターンが完結することが多い。JTAGテストでは、マイコン、FPGA、DSPなどのデバイスがプローブとして機能するため、物理的なプローブは不要である。メモリクラスタテストを実行するためには、マイコン、FPGAのバウンダリ・スキャンセルからDDRメモリのアドレス、データ、コントロールなどの全信号を制御する必要がある。メモリクラスタテストは、基板上のSRAM、DRAM、SDRAM、FIFOなどメモリに適用できる。

『JTAG ProVision』では、メモリの規格ごとにモデルライブラリが提供されるため、メモリの特性に合わせたテストプログラム、故障診断用の合否判定基準が自動生成される。図10のように、ピンレベルで故障箇所を特定できるため、製造ロットごとの故障傾向を製造にフィードバックすることできる。

### ●フラッシュメモリ、シリアルメモリ、PLDのオンボード書 き込み

JTAGテストツール『JTAG ProVision』では、フラッ

図10 テスト診断結果(IC-D200の20番ピンがオープン故障)

シュメモリ、シリアルメモリなどの部品ライブラリが提供される。メモリに適したコマンドを考慮したプログラムが自動生成されるため、ユーザーが書き込み用のプログラムを開発する必要がなくなる。『JTAG ProVision』では、メモリへの書き込み、コンペア、消去などを簡単に実行できる。したがって、生産ラインの1つの工程で基板検査から製品のプログラム書き込みまで行うことができる。

### ●JTAGテストのシーケンス

図 11 が標準的なJTAGテストのシーケンスである。 『JTAG ProVision』では、テストシーケンスの構築がドラック&ドロップの操作で簡単にでき、1クリックですべてのテストを実行できる。また、テスト結果のログファイルがHTML形式で自動的に保存される。

### ●JTAGテストを適用するメリット

エレクトロニクス製品の信頼性を向上させるため、初期不良はバーンイン試験のように被検査基板を高温で動作させ、初期不良にいたるまでの時間を加速し、初期不良を取り除くことができる。原因究明のためには、インサーキットテスタのような量産用テスト装置を使用する場合が多くみられる。しかし、室温で検査しても不良は発生しないことが多く、バーンイン試験とは異なったテスト結果になる。

このような検査結果の違いは、はんだ接合部の弱い部分 の温度感度によることが多い。高温でオープンとなるはん だ接合部は、温度低下またはピン治具の圧力により、正常な

状態に戻ることがある。JTAGテストは、テストインタフェースが簡単なため、温度を上昇させた状況でもテストと診断プロセスを適用することができる。そのため、JTAGテストは、バーンイン試験の効果を格段に改善でき、市場における不良発生率を大幅に減らすことができる。

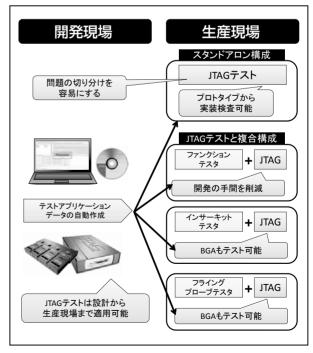

### ●所有している検査設備にJTAGテスト 機能を追加できる

一般的なプリント基板の量産製造ラインは、十分なテストカバレッジを保証するため、いくつかの検査手法の組み合わせによる補完テストを行っている。JTAGテストを導入している多くの工場では、すでに所有しているインサーキットテスタ、ファンクションテスタ、フライングリード

テスタの装置にJTAGテスト機能を組み込んで使用している。したがって、現行の製造ラインの中で、テストの工程を新たに追加することなく、JTAGテストによりBGA搭載基板を含む高密度基板をテストできることになる(図12)。

多くの実施可能なテストや検査手法(光学、X線、インサーキットテスト、JTAGテストなど)の組み合わせの選択は、いくつかの要因(テストする製品の特徴、プロダクションスループットの要求、予想できる不良範囲)に依存する。JTAGテストは、ICTのような他のテスト手法を補完するため、その組み合わせは予測できる不具合タイプに対し、最小のコストと最大限のカバレッジで最適のテスト手法を提供できる。

しかしJTAGテストとインサーキットテストの組み合わせは、すべてのアプリケーションに対して完全なテスト手法ではない。少量多品種の生産に対しては、JTAGテストとフライングプローブテスタを組み合わせるとコスト効果が大きくなることもある。もう一つは、ファンクションテストとJTAGテストの組み合わせがある。このテストシステムでは、1つの工程でファンクションテストとJTAGテスト、さらにオンボードプログラミングまで対応できる。

JTAGテストシステムは、スタンドアロン動作だけでなく、様々なテスト装置との組み合わせをサポートしている。アプリケーションへの移植が容易であり、工場設備に対してオフラインでテストプログラムの開発や故障診断ができるメリットは大きい。ユーザーが生産ラインを最適化するために、JTAG Technologies社はユーザーにカスタマイズ用のソフトウェアを提供している。たとえば、National Instruments社のLabView、LabWindowsやTestStandを使用したファンクションテストシステム用

図11 標準的なJTAGテストのシーケンス

のソフトウェアや各社インサーキットテスタやフライング プローブテスタを含むサードパーティのテストシステムに 対して、様々なソフトウェアとハードウェアを準備してい る。

### 3.あとがき

今回はJTAGテストとインサーキットテスタ、ファンクションテスタに焦点を絞り、生産ラインのコスト削減と品質向上に役立つヒント①から、ヒント⑤を紹介した。所有しているテスタにJTAGテストツールを組み込むことにより、検査カバレッジは飛躍的に向上することがお分かりいただけたと思う。生産ラインの1つの工程でJTAGテストも実行できるようになるため、検査コスト削減と品質向上を両立できる。

また、検査準備の段階においては、業界スタンダード 『JTAG ProVision』に登録されている10万種類を超える 部品ライブラリにより、テストプログラムが自動生成され、 基板検査の準備時間を大幅に短縮できる。

次号では『後編』として、光学検査装置(AOI)、X線検査装置を効率的に使用するためのJTAGテストの活用方法による生産ラインの効率化と企業内の各部門におけるメリットと具体的な利益の事例を紹介する。

図12 JTAGテストによる検査装置の補完