# 特集

# ゼロからわかる! JTAGバウンダリスキャン入門

アンドールシステムサポート(株) / 谷口 正純

#### はじめに

狭ピッチBGA部品が市場に広がり、0.8mmピッチのBGA パッケージでは製造不良が発生しなかった企業が、0.5mmおよび0.4mmピッチを使うようになり実装不良が急増している。 自動車メーカーが発表した情報では、0.8mmピッチから0.4mmピッチになると、はんだ量が12.5%になってしまうという。 このことからも、実装の難易度が劇的に高くなり、基板表面の汚れや異物、基板のひずみの影響を受けやすいことが分かる。

最近、設計部門、製造部門、品質保証部門、保守部門など、 あらゆる部門からBGA実装基板のテストと故障解析の方法 について相談を受けることが増えている。

JTAGテスト(バウンダリスキャンテスト)は、高密度実装基板のテストに使われるようになってきているが、具体的にどのような検査手法であるか知らない方が多い。

そこで、今回はIEEE1149.1スタンダードのバウンダリスキャンについて、初心者の方にも分かりやすく仕組みを解説する。

# 2

### 電子部品のパッケージの高密度化

電子部品のパッケージは高密度化が進んでいるが、過去に 遡って代表的な電子部品のパッケージ技術を紹介する。

図1に示すように、1970年代にプリント基板にピンを挿入するDIPパッケージが誕生した。電卓の普及に伴い、電子部品の多ピン化が求められるようになり、1977年にQFPパッケージ(Quad Flat Package)が誕生した。1980年代には、QFPの多ピン化と小型化が進んでいく。

1990年代には、携帯電話の普及に伴い、多ピン化と高密度化を実現するために、BGAバッケージ(Ball Grid Array)が誕生した。

図1 電子部品のパッケージの高密度化

現在のマイコン、SoC(System on a Chip)、FPGA (Field Programmable Gate Array)、メモリなどの電子 部品は、BGAパッケージが主流となっている。

BGAパッケージは、図1の右側のように部品の背面にはんだ付けするボール状のピンが配置されている。QFPパッケージのように、部品の四隅にピンを配置する必要がないため小型化できるメリットはあるが、プリント基板に実装後にははんだ付けの状態を確認することができないというデメリットがある。

携帯電話の高機能化に伴い、その後も電子部品の小型化が進み、CSPパッケージ(Chip Scale Package/Chip Size Package)ができた。2000年代になると携帯電話の高機能化に伴い、メモリ容量を拡大するためにメモリ素子を重ねるSIPパッケージ(System in Package)が誕生した。また、スマートフォンなどのモバイル機器向けにWLPパッケージ(Wafer Level Packaging)が誕生し、今後も高密度化するためのパッケージ技術は進化することが考えられる。

# 3

### 実装基板の変化

実装基板は図2のように、急速に高密度化が進んでいる。 左側の写真は、1980年代から1990年代までのDIPパッケージの部品が主流であり、プリント基板上のスルーホールに ピンを挿入してはんだ付けしていた。そのため、実装テストを 行うためには、当時主流だった電気検査のインサーキットテストのプローピンで容易にコンタクトすることができた。

しかし、近年のBGAパッケージとQFPパッケージから構成される右側の写真のような基板では、部品に対して直接プローブをコンタクトすることができないし、プロービングするためのテストパッドを基板上に設けることができなくなってい

1990年代の検査の課題

まにDIP部品から構成され

スルーホールの最もか中心でした

高密度な基板

プロープピンでコンタクトする

インサーキットテストに適した基板

プロープピンでコンタクトできないため

テストカバレッジが低下していた

図2 実装基板の過去と現在

る。さらに、マイコンとメモリ間のインターフェースが高速化 したため、配線上にテストパッドを設けてしまうと信号が反射 してしまい、信号品質が劣化してしまうためにテストパッドを設 けることができなくなった。

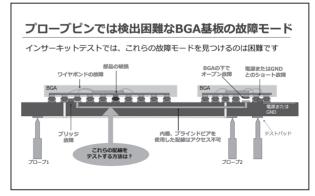

### BGA実装基板の故障モード

現在の製造現場において、BGA実装基板にどのような故障 モードが潜んでいるか、図3のBGA実装基板のイメージ図で 説明する。

この例では、プリント基板上にBGAパッケージの部品が2つ実装されている。BGA部品の故障には、部品内部のワイヤボンドの故障、部品の破損、ボールの破損などがある。また、部品実装後には、ボールとボールがショートしてしまうブリッジ故障、ボールと基板が接合しない状態となるオープン故障、ボールと電源、GNDとショートしてしまうブリッジ故障などがある。

従来のインサーキットテストを使用して、プローブピン1とプローブピン2をコンタクトした場合、テストパッド間の配線の導通は確認できる。また、アナログ回路のように、実装密度が低い回路であれば、プローブピンをコンタクトできるためインサーキットテストで実装保証ができる。しかし、BGAパッケージを中心としたデジタル回路、内層の配線などは検査することができない。

ブリッジ故障がある場合には、BGAのボールで故障しているのか、BGA以外の個所で故障しているか分からないため、 X線検査を用いても検出が困難である。また、はんだに亀裂が入ってしまいオープン故障がBGAのボール付近で発生していても、微細なクラックは非破壊ではX線CTの解像度を上げることができないため検出することができない。

図3 BGA基板の故障モードと従来の検査手法

# 5

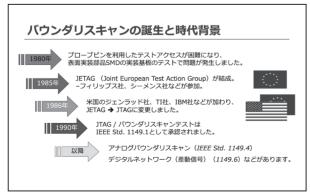

### バウンダリスキャンの誕生と 時代背景

1980年代にQFPパッケージの表面実装部品が市場に広まってきた頃、さらなる電子部品の小型化、高密度化が求められていたため、将来の実装基板のテスト方法が課題となっていた。

プローブピンではコンタクトできないとインサーキットテストやファンクションテストを行うことが困難になるため、図4の通り1985年にJETAG(Joint European Test Action Group)というワーキンググループが結成され、ヨーロッパのフィリップス社、シーメンス社などが中心となり、次世代の電気検査の手法が検討された。その翌年には、アメリカのジェンラッド社、テキサスインスツルメンツ社、IBM社などが加わり、JTAG(Joint Test Action Group、「ジェイタグ」と読む)という名称に変わり、新しいテスト規格を検討することが始まった。

1990年には、新しい電気検査の方法として、IEEE Std. 1149.1 規格として承認され、「JTAG/バウンダリスキャン・アーキテクチャ」が誕生した。このテスト規格は、JTAGテスト、バウンダリスキャンテスト、BST、JTAG Testingなどと呼ばれている。このJTAGというワーキンググループは解散したが、IEEEのワーキンググループとして引き継がれ、今も活動している。

規格は年々進化していて、最近ではセキュリティ対策用の ECID(Electronic Chip ID)が追加されている。また、アナログテスト用のバウンダリスキャン規格、差動信号用のバウンダリスキャン規格、オンボード書き込み用の規格などの派生規格も誕生している。

このバウンダリスキャンの規格を応用して、マイコンのデバッグ機能、FPGAの書き込み機能、フラッシュメモリの書き

込み機能などが実現されている。マイコン、FPGAなどの主な電子部品には、これらの機能が搭載されているため、回路設計者、ソフトウェア開発者にとっては、JTAGというキーワードは一般的なものになった。

# 6

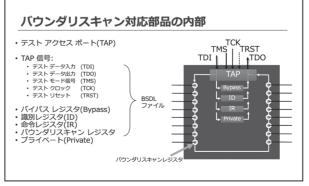

### バウンダリスキャンの仕組み

バウンダリスキャンに対応したマイコン、PLD、FPGAは、図5のような内部構成になっている。バウンダリスキャンに対応した部品には、バウンダリスキャン機能を制御するためのテストアクセスポート(TAP)と呼ばれる機能が内蔵されている。

バウンダリスキャン規格では、TAPを制御するために、TAP信号もしくはJTAGポート、JTAG信号と呼ばれているTDI、TDO、TMS、TCK、TRSTの5本の信号が定義されている。TAPの制御と、複数のバウンダリスキャン対応部品を同期しながらテストをするために、TCKと呼ばれるテスト用のクロック信号がある。

また、TAPのモードを選択するために、テストモードセレクトTMSとテストリセットTRSTがある。TRSTは、オプションの信号のためバウンダリスキャン対応の電子部品によっては、JTAGポートに4本の信号しかない場合もある。

バウンダリスキャン対応部品には、テストを実行するための レジスタという記憶回路がある。TAPはレジスタに記憶され た命令とデータを使って、様々なテスト機能を制御する仕組み になっている。

バイパスレジスタ (Bypass)は、バウンダリスキャンデバイスのバウンダリスキャンの機能を使用しない場合に有効になる。 TDIから入力されたテストデータは、バウンダリスキャンレジスタを通過せずに、Bypassレジスタから短時間でTD0に出力させることができる。

図4 バウンダリスキャンの誕生

図5 バウンダリスキャンの仕組み

IDレジスタには、部品の識別番号が記憶されている。バウンダリスキャン対応部品を実装した後で、正しい部品が実装されているかテストするために使用される。このレジスタは、オプションであるが、殆どのバウンダリスキャン対応部品にIDレジスタがあり、メーカー名、型番、リビジョンなどの情報が保存されている。

IRレジスタは、バウンダリスキャンの機能を実行するためのインストラクションレジスタ(命令レジスタ)である。このレジスタに特定のデータを与えると、バウンダリスキャンの機能が実行される。

バイパス命令やIDコード命令のほかに、バウンダリスキャンレジスタの状態をサンプリングする命令、テストを実行するための命令などが定義されている。また、オプション命令を自由に定義することができるようになっている。

バウンダリスキャンレジスタ (バウンダリスキャンセル)は、バウンダリスキャン対応部品のIOピンごとに配置されている。電気試験をするための信号を出力したり、入力 (スキャン)したりするためのレジスタである。IRレジスタにセットしたデータにより、バウンダリスキャンレジスタが機能する仕組みになっている。

バウンダリスキャンレジスタが、どのピンに配置されているかは規格では定められていないため、電子部品により異なっている。したがって、実装基板のテストカバレッジに最も影響を与えるのが、このバウンダリスキャンレジスタということになる。

バウンダリスキャンレジスタがスキャンしたデータは、TDIからテストデータをシフトしていき、バウンダリスキャンレジスタを通過してTDOから出力され、JTAGコントローラからパソコンへ転送される。JTAGテスト用のソフトウェアでは、回路図のデータから生成された期待値と比較して合否判定が行われる。

プライベート命令は、部品メーカーが自由に定義することができるようになっている。このプライベート命令は、セキュリティ機能、デバッガのエミュレータ機能(JTAG ICE)、フラッシュメモリの書き込み機能などに使われている。

TAPの機能と各レジスタの定義は、部品メーカーから提供されるBSDLファイル (Boundary Scan Description Language File)に制御方法が記述されている。BSDLファイルはIEEE1149.1 規格で定められたフォーマットで記述されていて、部品メーカーのホームページからダウンロードできる。

BSDLファイルはテキストエディタで開くと、バウンダリスキャンレジスタの配置と命令レジスタの機能、設計上の注意

点を確認することができる。BSDLファイルの確認方法は、 JTAG技術レポート第2号を参考にして欲しい。

(https://www.andor.jp/wp-content/uploads/pdf-itag-tec-r2.pdf)

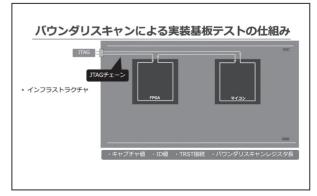

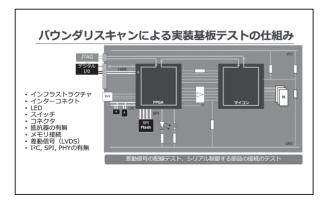

### バウンダリスキャンによる 実装基板テストの什組み

バウンダリスキャンを活用した実装基板検査の仕組みを、図6のようにバウンダリスキャン対応部品のマイコンと FPGAが、2つ実装されている基板の例を用いて解説する。

基板上に2つのバウンダリスキャン対応部品がある場合には、JTAGチェーンと呼ばれるTDIとTDOを配線して、JTAGポートを1つにまとめることができる。部品ごとにJTAGポートを分けてテストすることもできる。

#### 1. インフラストラクチャーテスト

最初にテストするのは、インフラストラクチャーテストという バウンダリスキャンの基本的なテストで、バウンダリスキャン機 能が正しく動作するかをテストする。

JTAGチェーンからバウンダリスキャン対応部品のレジスタの値を読み、初期値と比較して合否判定を行う。ID番号などのレジスタ値が、BSDLファイルに記載されている値通りに正しく読めれば、JTAGポートとJTAGチェーン、バウンダリスキャン機能が正しく機能することを確認できる。また、バウンダリスキャンレジスタ長がBSDLファイルで定義された通りに正しいこともテストする。

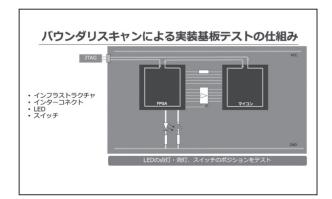

#### 2. インターコネクトテスト

インターコネクトテストでは、バウンダリスキャンデバイス

図6 インフラテストの仕組み

### Face Face III

同士の配線をテストする。図7のように、FPGAとマイコンが直接つながっている配線のテストのほかに、抵抗が直列で繋がっている場合の抵抗を含めた配線のテストができる。また、バッファなどのロジック部品を介して接続されている配線についてもテストができる。

検出できる故障モードは、オープン(はんだの未接合、パターン断線、足浮きなど)、ショート(信号同士のブリッジ)、スタックアット 1 (電源とのブリッジ)、スタックアット 0 (GNDとのブリッジ)などがある。

#### 3. LEDとスイッチのテスト

LEDのテストは、図8のようにバウンダリスキャンレジスタからLEDを駆動して、点灯・消灯を行うことができる。 テストの合否判定は、検査員の目視またはLEDアナライザなどのセンサ、カメラによる画像診断で観測する必要がある。

スイッチのテストは、スイッチのONとOFFのポジションをバウンダリスキャンレジスタで読み取ることができる。例えば、テストデータに、製品出荷時のDIPスイッチのポジションを設定しておけば、出荷テストでスイッチの状態もテストすること

バウンダリスキャンによる実装基板テストの仕組み

・インフラストラクチャ

・インターコネクト

オーブン・ショート・スタックアット1・スタックアット0 を検出可能

図7 インターコネクトテストの仕組み

図8 LEDとスイッチのテスト

が可能となる。

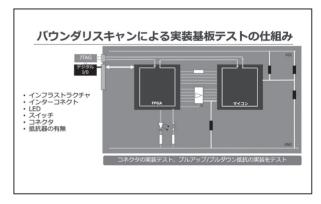

#### 4. コネクタと抵抗のテスト

コネクタのテストは、図9のように検査治具にバウンダリスキャンテスト用のデジタルI/Oを接続してテストを行う。 FPGAのバウンダリスキャンレジスタから信号を出力して、コネクタの外部に接続したデジタルI/Oでスキャンして合否判定を行う。検査治具を使用しない場合には、折り返しケーブルをコネクタに接続して、バウンダリスキャンレジスタの出力と入力の関係を作ることにより、コネクタの実装テストができる。

プルアップ抵抗、プルダウン抵抗のテストは、バウンダリスキャンレジスタから信号を入出力させて抵抗をテストする仕組みである。 バウンダリスキャンは、デジタルのテストであり、抵抗値は確認できないが、チップ抵抗の有無、浮き、ずれ、はんだ不良によるオープン、抵抗の短絡(ゼロオーム)をテストできる。

プルアップ抵抗とプルダウン抵抗は、マイコンやFPGAの モード設定に使用されるが、抵抗の実装不良によりファンク

図9 コネクタと抵抗のテスト

図10 メモリのテスト

ションテストが起動しない基板のテストと故障解析にバウンダリスキャンテストは有効である。

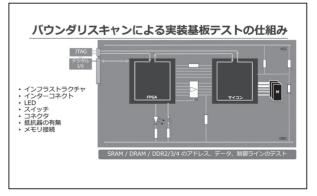

#### 5. メモリのテスト

メモリのテストは、図10のようにバウンダリスキャンレジスタから、メモリにテストデータを書き込み、正しくテストデータを読み出せるかテストする。SDRAM、DRAM、DDR2、DDR3、DDR4などがテスト対象となり、故障診断の結果でアドレスバス、データバス、制御信号のどこに不良があるか自動的に診断される。

現在、DDRメモリに関する実装不良が増えており、ピンポイントで不良個所がわかるバウンダリスキャンは、故障解析の有効な手段となる。

#### 6. 差動信号LVDSとSPI、I2Cのテスト

高速差動回路の配線は、図11のようにIEEE1149.6というバウンダリスキャンの派生規格でテストすることができる。 FPGAは、IEEE1149.6に準拠した部品が多く、送信側からカップリングコンデンサを通過するパルス波を発生させて、受信側でスキャンして合否判定する。

SPI、I2Cなどのシリアルインタフェースのテストは、バウンダリスキャンレジスタからシリアルインタフェースを制御して、SPIのフラッシュメモリ、I2Cのセンサ、A/Dコンバータなどをテストできる。

JTAG Technologies社のJTAG ProVisionでは、Python スクリプト言語を使って、バウンダリスキャンレジスタからシリアルインターフェースにアクセスするためのライブラリが用意されている。 例えば、A/Dコンバータの値が指定する電圧の範囲内であるか判断して、合否判定を行うことができる。

図11 差動信号とI2C、SPI信号のテスト

## まとめ

バウンダリスキャンの仕組みを難しく感じた方も多いのではないだろうか。しかし、実際に基板の検査を行う際には、ユーザーはテスト対象の基板の回路図 CADから出力される配線情報 (ネットリスト)と部品表、部品メーカーのホームページからダウンロードできる BSDLファイルをJTAGテストツール「JTAG ProVision」にインポートして、ウイザードに従って操作していくとテストデータが自動生成され準備ができる。JTAGテストツールが、テストの実行から故障診断まで自動的に実行してくれるので、バウンダリスキャンの詳細な仕組みは理解しなくても問題ない。

当社では、JTAGラーニングセンターを立ち上げ、今回解説した「バウンダリスキャンの基礎」のほかに、基礎コースの「バウンダリスキャンの詳細」、「テストカバレッジの評価」、応用コースの「エミュレーティブテスト」、「デバイスプログラミング」、「ファンクションテストJFT」など、JTAGバウンダリスキャンを体系的に学ぶことができるオンデマンドセミナーを提供しているので、BGA実装基板でお困りの際は活用して欲しい。(https://www.andor.jp/jtag/jtag-webinar/)

設計者がJTAGテストの効果を測定する際には、図12の「JTAGテストの効果測定ガイダンス」を参考にして、テスト対象基板のテストカバレッジを評価すると良い。回路設計後に効果測定することで、テスト容易化設計を考慮することができる。回路の工夫により、テストカバレッジを最大化できれば、故障解析の精度が格段に向上させることができる。

図12 JTAGテストの効果測定ガイダンス