# バウンダリスキャン・テストと DFT~テスト範囲向上のための設計 其の志~

#### まえがき

前回、DFT(Design For Test)について、JTAG のシステムレベル・テストについてご紹介しました。

今回からは、もっと 前段階のお話設計 時に陥りやすい 題点をが対策につい 注意点などについ などに分けて 取り上げてみたいと 思います。

まず、初回はバウンダリスキャン・デバイスの注意点について、お話ししてみたいと思います。

## まずは BSDL ファイル入手から!

皆さんもご存じのように、JTAG テストを行なうためには、『バウンダリスキャン・デバイスを使用した設計を行なう』という前提条件があります。

このバウンダリスキャン・デバイスには、デバイス毎に、バウンダリスキャンの仕組みを定義した『BSDLファイル(Boundary-Scan Discription Langage file)』 という ASCII 形式ファイルがあり、デバイス・ベンダから無償で供給される仕組みとなっています。

JTAG テストを行うためには、この BSDL ファイルをまず入手する必要があります。

FPGA やcPLD などの場合、デバイス・ベンダのホームページより入手できるケースが多いようですが、ASIC(Application Specific Integrated Circuit)デバイスや特定用途向けの一部のデバイスなどは NDA 契約(機密保持契約)をしていないと入手できないというケースもあるようです。

では、この BSDL ファイルはいつ入手したら良いので しょうか?

答えは、

「ご設計前に必ずご入手いただくこと!」です。

理由としては、『BSDL ファイルには非常に重要なことが記載されている』からです。

#### BSDL ファイル、ここを見るべし!

デバイスによっては、バウンダリスキャン機能を動作させるために「特定ピンに対して固定値を与えないとならないケース」や「バウンダリスキャン機能を使用する際に注意点があるケース」があります。

このような場合には、一般的には BSDL ファイル内に、 その旨が記載されています。

まずは、次の例をご参照ください。

#### 『attribute DESIGN\_WARNING』の例

attribute DESIGN\_WARNING of SA1110: entity is

"1. IEEE 1149.1 circuits on SA1110 are designed"

"primarily to support testing in off-line module"

"manufacturing environment. The SAMPLE/PRELOAD

"instruction support is designed primarily for "&

"supporting interconnection verification test "&

"and not for at-speed samples of pin data. "&

"2. Ensure to drive BATTF and VDDF to logic level 0 "&

"else the chip will sleep! ";

この『DESIGN WARNING』というキーワードには、注 意すべき点が英語の文章で記載されています。

この例の場合は、「BATTF と VDDF 信号ピンがロジック"0"状態でないと、チップがスリープモードに入ってしまう」ことがわかります。

つづいて、次の例をご参照ください。

#### 『attribute COMPLIANCE PATTERNS』の例

attribute COMPLIANCE\_PATTERNS of XC2S150\_FG456 : entity is "(PROGRAM) (1)";

この『attribute COMPLIANCE\_PATTERNS』というキーワードには、バウンダリスキャン機能を動作させるために固定値を与えないとならないピンや値が記載されています。(前括弧内に信号名、後括弧内に与えるべき値が記載されています。)

例の場合は、「PROGRAM ピンに対してロジック"1" を与えないといけない」ということがわかります。

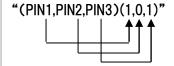

複数のピンに対して処理が必要な場合は、次例のように記述します。

#### 例)

PIN1=1, PIN2=0, PIN3=1 というように、値を与えます。

このように、BSDL ファイルの

に注意を払うことが重要です。

#### プロセッサは特に注意すべし!

MPU, CPU, DSP などと呼ばれるプロセッサ・デバイス の場合は、特に以下の点にご注意ください。

#### (1) JTAG テスト対応の確認

プロセッサの場合、ソフトウェアやハードウェアの開発目的のために、JTAG インターフェイスを使用したデバッガ(JTAG エミュレータなどと呼ばれる製品)を使用することがあります。このようなデバッグ機能として使えるケースでも、JTAG テストには対応していないデバイスも存在します。

### (2) 各種モードとバウンダリスキャン機能

プロセッサは、電源投入手順やクロック供給、リセット処理などが正しく行われていないと、正常に動作しません。また、バウンダリスキャン機能も一緒に動作しないケースがあります。

また、多くの場合は、サスペンド・モードやスリープ・ モードなどの省電力機能がデバイスに搭載されてい るため、それらの動作モード下ではバウンダリスキャ ン機能も停止してしまうようです。

そのため、テスト時には、これらの動作モードに入らないように注意する必要があります。

プロセッサをテストする場合は、以下の点が回路図 上でどのようになっているかをご確認ください。

- ・クロック供給

- ・リセット

- ウォッチ・ドッグ・タイマー

- ・サスペンド/スリープ・モード

- ・割り込み・・・

このような点は BSDL ファイルに記載されておらず、 データシートの情報を調べないとわからないというケースが多くあるようです。

設計時には、BSDL ファイルを入手するのと一緒に、 データシートの「JTAG テスト」についての注意点を見 る習慣をつけることをお勧めします。

#### あとがき

まず、始めの一歩として、デバイスに関する注意点について説明しました。

「JTAG テストって、結構大変なのでは?」なんて、身構えないでください。

設計段階で、ほんの少し注意するだけで、今まで不 良基板に悩まされてきた煩わしさを解消することが できるのです。こんな便利な機能を使わずに放って おくなんて、勿体ないと思いませんか?

〈山田 実〉