# JTAG バウンダリ スキャンと DFT

~テスト範囲向上のための設計 其の弐~

#### まえがき

前回に引き続き、今回も JTA バウンダリ スキャン・テスト(以下、JTAG テストと記載)についての DFT(Design For Test)として、設計段階に注意する点をご紹介したいと思います。

JTAG テストを行うためには、JTAG の制御信号である TAP(Test Access Port)信号を基板外部に引き出し、バウンダリ スキャン・コントローラと接続することになります。

※ バウンダリ スキャン・コントローラは、JTAG テストを制御するための専用ハードウェアです。

IEEE Std. 1149.1 規格(以下、Dot1 規格と記載)では、TAP の接続方法についての詳細は記載されておらず、基板にコネクタを実装する、テストパッドを配置するなど、接続方法はユーザーに委ねられています。しかしながら、この接続には幾つかの注意点があります。ここでは、それらについて説明します。

#### TAP 信号の誤動作と終端処理

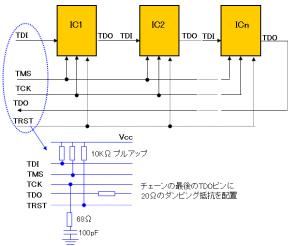

TAP 信号には、図1のような終端処理をすることをお勧めします。

図 1. TAP 信号の終端処理

この終端処理をするのは以下の理由からです。

※ ここでは、弊社が扱っている JTAG Technologies 社のバウンダリスキャン・コントローラを元に記載しているため、他社製ツールでは抵抗値などが異なるケースがあります。

# (1) TDIとTMS のプルアップ

Dot1 規格では、誤動作を防止するために、 TDI(Test Data Input)端子と TMS(Test Mode Select)端子はデバイス内部にプルアップ抵抗を 搭載することを推奨しています。

バウンダリ スキャン・コントローラを基板に接続しない際に誤動作をすることを防ぐための処理です。デバイス内部のプルアップ・レベルが低いケースなどを考え、デバイス外部へプルアップ抵抗を接続することをお勧めします。

#### (2) TRST のプルアップ

TRST(Test ReSeT)端子についても、Dot1 規格ではデバイス内部にプルアップ抵抗を搭載することを推奨しています。

前述の TDI と TMS と同様に、バイス外部にプルアップ抵抗を接続することをお勧めします。

デバイスによっては、データシートに「JTAG テスト未使用時は、TRST 端子をプルダウン抵抗と接続する」という内容が記載されているケースがありますが、その際は、データシートに従った処理をしてください。

TRST 端子をアクティブにしないとバウンダリス キャン機能が動作しないというデバイスも存在 するため、TRST 端子を持つデバイスは必ずバ

ウンダリ スキャン・コントローラと接続するような回路とすることをお勧めします。

# (3) TDO のダンピング抵抗

デバイスのスキャンチェーンの最終段の TDO(Test Data Output)端子の間近にダンピング 抵抗(シリーズ抵抗)を接続することをお勧めしま す。これは、信号の反射を防ぐための処理です。

(4) TCK ラインの抵抗とコンデンサ接続 TCK(Test ClocK)端子には、抵抗とコンデンサを 介して GND と接続することをお勧めします。これ は、バウンダリ スキャン・コントローラと接続す る際のインピーダンス・マッチングをさせるため の処理です。

#### TAP 信号のバッファリング

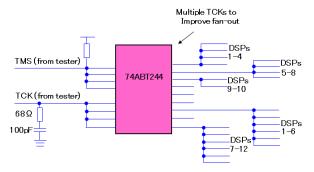

次に、TAP 信号のバッファリングについて説明します。

図 2. TAP 信号のバッファリング

スキャンチェーン内に幾つかのデバイスが接続されている場合には、TCK 端子と TMS 端子のそれぞれの端子は各デバイスに対して複数の接続がされることになります。そのため、Fan-In と Fan-out の関係から、バウンダリ スキャン・コントローラのドライブ能力が足りず、正常に動作しないデバイスが発生することが考えられます。

バウンダリ スキャン・コントローラの TAP 接続ライン の直後にバッファ・デバイスを設け、各デバイスを分岐させた接続とすることをお勧めします。

## TAP 信号の物理的バイパス

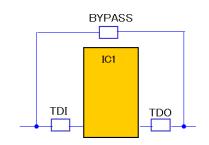

新規デバイスなど、使用実績がないデバイスを使う際は、そのデバイスをスキャンチェーンから物理的にバイパス出来るような回路を、試作時に組み込んでいただくことをお勧めします。

図 3. TAP 信号の物理的バイパス

図 3 の TDI、TDO および BYPASS と書いてある口印 部分は、 $0\Omega$ 抵抗を意味しています。

次のように 0Ω抵抗を実装することで、スキャンチェーン内にデバイスを含めたり、外したりすることができるようになります。

- (1) スキャンチェーンに含めたい場合 TDI、TDO は接続。BYPAS は未接続。

- (2) スキャンチェーンから外したい場合 TDI、TDO は未接続。BYPASS は接続。

## あとがき

毎回毎回、文章が長くなってしまう傾向が見られる 本レポートですが、ご理解いただけますようお願いい たします。

次回は、スキャン・チェーンの分断や、FPGA デバイス使用時の注意など、もう少しだけ DFT という点について書いてみたいと思います。

〈山田 実〉