バウンダリスキャン

JTAG / バウンダリスキャン インターフェイスとテクノロジーは、今日のほとんどの電子機器に搭載されています。このテクノロジーは1990 年に標準化されました。それ以来、JTAG / バウンダリスキャンのテストカバレッジを拡張するために、元の標準に基づいてさらに多くの標準が追加され、元の標準を強化してきました。

私たちは、本物の JTAG バウンダリスキャンであることを誇りに思っています。

当社のプロフェッショナルなバウンダリスキャンハードウェアおよびソフトウェアのテストおよびプログラミングソリューションは、実績があり、信頼性が高く、高速なテスト ソリューションを求めるお客様のニーズに合わせてカスタマイズされています。

JTAGバウンダリスキャンとは

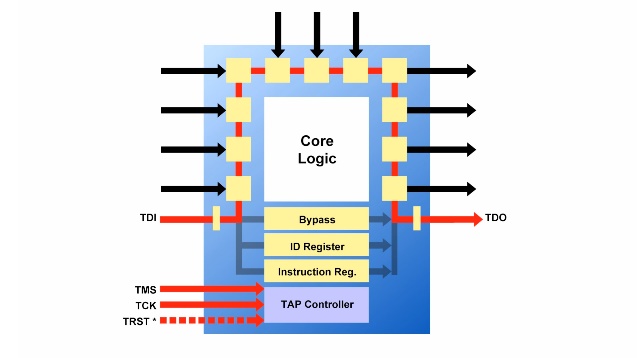

JTAG / バウンダリスキャン (IEEE Std 1149.1) は、今日の多くの ICチップ上の特殊な組み込みロジックへのアクセスを可能にする4本の信号から構成されるシリアルJTAG インターフェイスです。

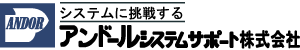

JTAG アクセス可能なロジックインターフェイスは、次のいずれかまたはすべてを含む多くの機能を提供します。

- 物理的な外部プローブなしでデバイス間の接続をテストするためのテストロジック

- デバイスのオンボードプログラミングのためのフラッシュメモリ、CPLD、およびFPGAのプログラミングロジック

- ソフトウェアのデバッグや、組み込みソフトウェアを使用せずに周辺デバイスとの接続を高速でテストする場合、またはマイクロコントローラの組み込みフラッシュをプログラムする場合に使用される、マイクロプロセッサおよびマイクロコントローラのデバッグロジック

JTAG / バウンダリ スキャン インターフェイスとロジックを備えたデバイスは、今日のプリント基板アセンブリ (PCBA) の多くに搭載されています。多くの場合、デバイスはシリアル (デイジーチェーン) 形式で接続され、PCBA 上にいわゆる「スキャンチェーン」を形成します。外部に接続した JTAG / バウンダリスキャン コントローラーを使用してロジックをアクティブにし、実装基板のテストとデバイスのプログラミングを完了します。JTAG / バウンダリスキャン ロジックを使用すると、外部のプロービングや複雑な検査治具が不要になるため、設計、製造、サービスにおけるボードのテストやデバイスのプログラミングに使用する機器と複雑さを最小限に抑えられます。

このように、JTAG / バウンダリスキャンは、実装基板テストとプログラミングシステムの時間とコストを節約できるため、企業にとって非常に重要になります。

バウンダリスキャンを行う理由

JTAG バウンダリスキャンは、組織の時間の節約、コスト効率の向上、製品の品質の強化という 3 つの方法でプロセスを支援します。その方法を説明するために、いくつかの詳細を見てみましょう。

JTAG バウンダリスキャン規格は、従来の PCB アセンブリのテスト装置が直面する基本的な技術的問題、つまり、ファインピッチ、多ピン SMD パッケージ (特に BGA) のデバイスピンへのプロービングを解決するために開発されました。チップに JTAG / バウンダリスキャン ロジックを組み込むことにより、ピンに簡単にアクセスできるようになり、パッケージの種類やデバイスの複雑さに関係なく、外部プロービングなしでテスト信号をデバイス間で送信できるようになります。

製品の品質を保証するにはテストが不可欠です。1つの可能性は、機能テストを実行することです。ただし、機能テストには2つの主な欠点があります。1つは、考えられるすべてのアセンブリの欠陥をカバーしたかどうかがわからないこと、もう1つは、障害が見つかった場合でも、その原因を診断するのが難しく、(時間とコストがかかることです。これら2つの欠点は、構造テスト(実装テスト、ストラクチュアルテスト)によって解決されます。

ただし、構造テストではデバイスのピンを調査する必要があります。小型化に伴いプロービングができなくなり、外部プローブを用いた構造検査が不可能になります。バウンダリスキャンを使用すると、そのような外部プローブは必要なくなります。したがって、バウンダリスキャンは、小型化の場合でも構造テストが可能な方法として開発されました。

つまり、バウンダリスキャンは、小型化の場合でも構造テストを容易にするために開発されました。

元の規格はボードのテストに焦点を当てていましたが、JTAGインターフェイスはすぐにデバイス (フラッシュ メモリ、FPGA、CPLD、マイクロコントローラー) のインシステムプログラミング(オンボード書き込み)にも使用されるようになりました。JTAG / バウンダリスキャン規格には、従来のシステムに比べて多くの利点があります。

テスト

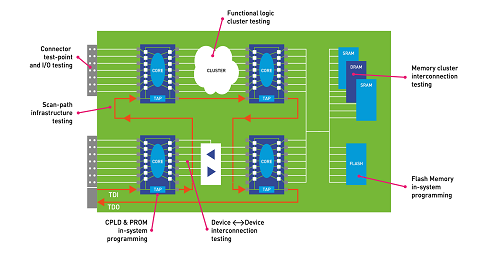

実装基板(プリント基板アセンブリPCBA) 上のピンや信号にアクセスするためにプロービング技術を使用する従来のテスト機器は、ますます多くの課題に直面しています。まず、表面実装デバイス (SMD)、特にボールグリッドアレイ (BGA) パッケージの使用が増加しているため、デバイスのピンとネットの外部プローブがますます複雑になっています。第2に、システムオンチップ (SoC) デバイスを実現する単一チップへの機能の統合が進行しているため、デバイスの複雑さが増大し、外部制御がますます困難になっています。その結果、これらのテクノロジを使用するボードでは、従来のテスト方法で可能なテストカバレッジと診断解像度が低下します。JTAG経由でアクセスできる実装基板の部分が増加すると、JTAG経由のテストカバレッジと診断解像度の両方が増加します。

ボード上で JTAG デバイスが使用されていない場合は、当然のことながら、ボードのテストとプログラムに従来のテスト方法のみを使用できます。ただし、JTAG デバイスが実装基板上で使用されている場合は、その機能をテストとプログラミングに使用できます。ボードの設計と JTAG アクセスの割合によっては、JTAGベースのテストツールとプログラミングツールだけで、ボード全体のテストとプログラミングが十分に行える場合があります。JTAGを介してボードの一部のみにアクセスできる場合は、従来のテスト方法と JTAG を組み合わせることで、高いテストカバレッジが得られます。

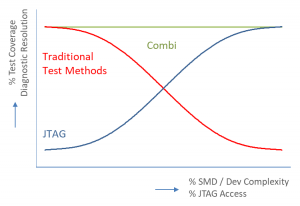

チップ内のJTAGロジック

JTAG インターフェイスを介してアクセスできるチップ内の組み込みリソースの例には、バウンダリスキャン レジスタやマイクロコントローラ デバッグ ロジックなどがあります。

バウンダリスキャン レジスタにより、デバイス機能 (デバイスコア) を使用せずにデバイスのピンに直接アクセスできます。テストやプログラミングのために、異なるデバイス間の接続に簡単にアクセスできます。バウンダリ スキャン レジスタは、バウンダリスキャン テストとプログラミングの中心です。マイクロコントローラー デバッグレジスタ/ロジックにより、マイクロプロセッサー機能を使用せずにマイクロプロセッサーのバスに直接アクセスできます。

デバイスのプログラミング

JTAG インターフェイスはテストに使用できるだけでなく、実装基板上のデバイスをプログラムするためのJTAG プログラマとしても使用できます。フラッシュメモリ、FPGA、CPLD、マイクロコントローラ (組み込みフラッシュ)、および I2C、SPI、PMBus デバイスなどのシリアルデバイスは、4つの信号から構成されるJTAG インターフェイス、または周囲の JTAG デバイスを介してプログラムできます。JTAGを使用すると、このようなデバイスを PCBに実装した後にプログラムすることができます。このオンボード プログラミング、つまりインシステムプログラミング (ISP) の結果は次のとおりです。

- デバイスの在庫はプログラムされていない部品のみにすることができ、製造時の物流を大幅に簡素化

- デバイスを複数回ではなく1回で処理

- 製品のアップグレードなど、現場でも簡単に再プログラミング可能

JTAGのシリアル特性により、大規模フラッシュデバイスのプログラミングは非常に遅くなる可能性があります。これは、フラッシュ部分にプログラマブル ロジックデバイス (FPGA など) が接続されている場合、Provisionなどを使用してプログラミングのプロセスを大幅に高速化し、デバイスの最大速度に達することがよくあることを意味します。

当社のソリューションは、オンボードのFPGAの内部回路を使用して、シンプルなフラッシュプログラマを作成します。これにより、制御ビット、アドレスビット、データビットのシフトなど、帯域幅が制限された反復タスクの JTAG スキャンチェーンが軽減されます。スキャンチェーンからトラフィックを削除することで、ソリューションは特定のフラッシュメモリ デバイスに対して理論上に近いプログラミング時間を達成できます。

インシステム デバイスプログラミングの詳細については、「インシステム デバイス プログラミング ガイド」を参照してください。

IEEE 規格に準拠した規格

シリアルインターフェイスとロジックは、もともと1980年代後半を通じて、JTAG (Joint Test Action Group) として知られるフィリップス、BT、GEC、TI などのテスト専門家のグループによって開発されました。このグループは、IEEE ワーキンググループとして継続して最終規格を完成させ、その最終規格が正式名IEEE Std 1149.1、IEEE スタンダードテスト アクセスポート (JTAG インターフェイス)、およびバウンダリスキャン アーキテクチャとなりました。この規格は1990年に初めてリリースされました。それ以来機能拡張が行われ、最新の更新は2013年に行われました。IEEE 1149.1-2013 を参照してください。

IEEE Std 1149.1 は、JTAGテスト、JTAG、JTAGバウンダリスキャン、BST、Dot1などの別名で呼ばれることもよくあります。JTAGデバイスは、正式には IEEE 1149.1準拠デバイスと呼ばれます。

この規格では、テストアクセスポート (TAP) と呼ばれるシリアル (JTAG) インターフェイスと、チップに組み込まれるテストロジック アーキテクチャが定義されています。テストロジックの具体的な例の1つは、実装基板上のデバイス間の接続をテストするために、いわゆるバウンダリスキャン レジスタと呼ばれる規格で定義されています。

TAPは4つ(場合によっては5つ) の信号を備えています。

- TCK(テストクロック)

- TMS (テストモード セレクト)

- TDI (テストデータ インプット)

- TDO (テストデータ アウトプット)

- TRST (テストロジックリセット) (オプション)

実装基板内のテスト インフラストラクチャを簡素化するには、最初のデバイスの TDO が次のデバイスのTDIに接続されて、いわゆるスキャンチェーンを形成するようにデバイスをシリアル (デイジーチェーン) 形式で接続する方法が一般的です。

テストロジック アーキテクチャは、1つの命令レジスタ (IR) と複数のデータ レジスタ (DR) で構成されます。IRスキャンでIRにオペコードをロードすることにより、特定のDRが選択され、その後、連続したDRスキャンでアクセスされます。

バウンダリスキャン レジスタがDRとして選択されている場合、このレジスタはデバイスの主要なコア機能を分離しながらデバイスのピンを制御します。

Dot1のテストロジック アーキテクチャは、他のデータレジスタ (DR) をチップ設計に簡単に追加できるように定義されています。たとえば、マイクロプロセッサやマイクロコントローラのデバッグロジック、または最新の CPLDやFPGAのプログラミングロジックなどです。これらのDRは、元のDot1に基づいて構築され、拡張された追加の標準で定義されています。