マルチ・バス・スイッチ・マトリックスを使用した大規模半導体パラメトリック・テストの高速化

変化が速く競争の激しい半導体業界では、革新的な新製品設計を市場に投入するまでの時間が非常に重要です。しかし、サプライヤーのブランド評判がかかっているため、デバイス開発段階で広範囲にわたるテストを実施し、さまざまな厳しい顧客環境でも一貫して機能する必要がある製品のあらゆる側面の長期的な信頼性を確保する必要があります。

信頼性の検証には、高加速ストレス・テスト(Highly Accelerated Stress Testing)に基づく長いプロセスになることがあります。このテストでは、DUT(device under test)となるテスト対象の半導体デバイスが故障するまで、温度、湿度、機械的ストレスなどの極端な環境条件にさらします。その後、故障のメカニズムを調査し、潜在的な問題を修正します。

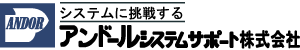

適用される各ストレスサイクル中またはその後、DUTは通常、何らかの形式のパラメトリック・テストを受けます。これには、半導体ウェハーまたはパッケージ基板上に製造された専用のテスト構造の電気的テストと特性評価が含まれ、特定の構造が依然として必要な設計基準を満たしているかどうかが検証されます。これらのテストは通常、ソース/測定ユニット (SMU) によって実行され、単純な抵抗測定から、スキャンされた電流対電圧 (IV) または静電容量対電圧 (CV) 測定までの範囲にわたります。通常、図1に示すように、ケルビン4線接続を介して行われ、機器とDUTの相互接続抵抗を排除します。

図1 ケルビン4端子抵抗測定構成

たとえば、最新のサーバー向けのCPUパッケージをテストする場合、DUTピンの総数は数百、数千に達する可能性があります。そのため、各パラメトリック・テストで DUT ピンのペアに SMU を順番に迅速かつ確実に接続するために、ピン数の多い自動スイッチング・システムが必要です。4線式測定では、ピンごとに2つの個別のテスト接続が必要です。

IC設計者は、品質を犠牲にすることなく信頼性テストを加速しようと常に努力しているため、多数のDUTピンのテスト時間を最小限に抑えるようにパラメトリック・テスト システムを設計する必要があります。この目標を達成する比較的簡単な方法の1つは、2つのSMUを異なるDUTピンのペアに並列に接続し、それらのパラメトリック測定を同時に記録して、全体のテスト時間を実質的に半分にすることです。この戦略に基づいて、ピカリング社では大手半導体メーカーと緊密に連携し、最大12個のSMUをDUTに並列に同時に接続することで、非常に高速な4線式パラメトリック・テストに特化して最適化された、ピン数の多いスイッチ・マトリックス・プラットフォームを開発しました。

ピカリング社のモジュラー・スイッチ・マトリックス・プラットフォーム

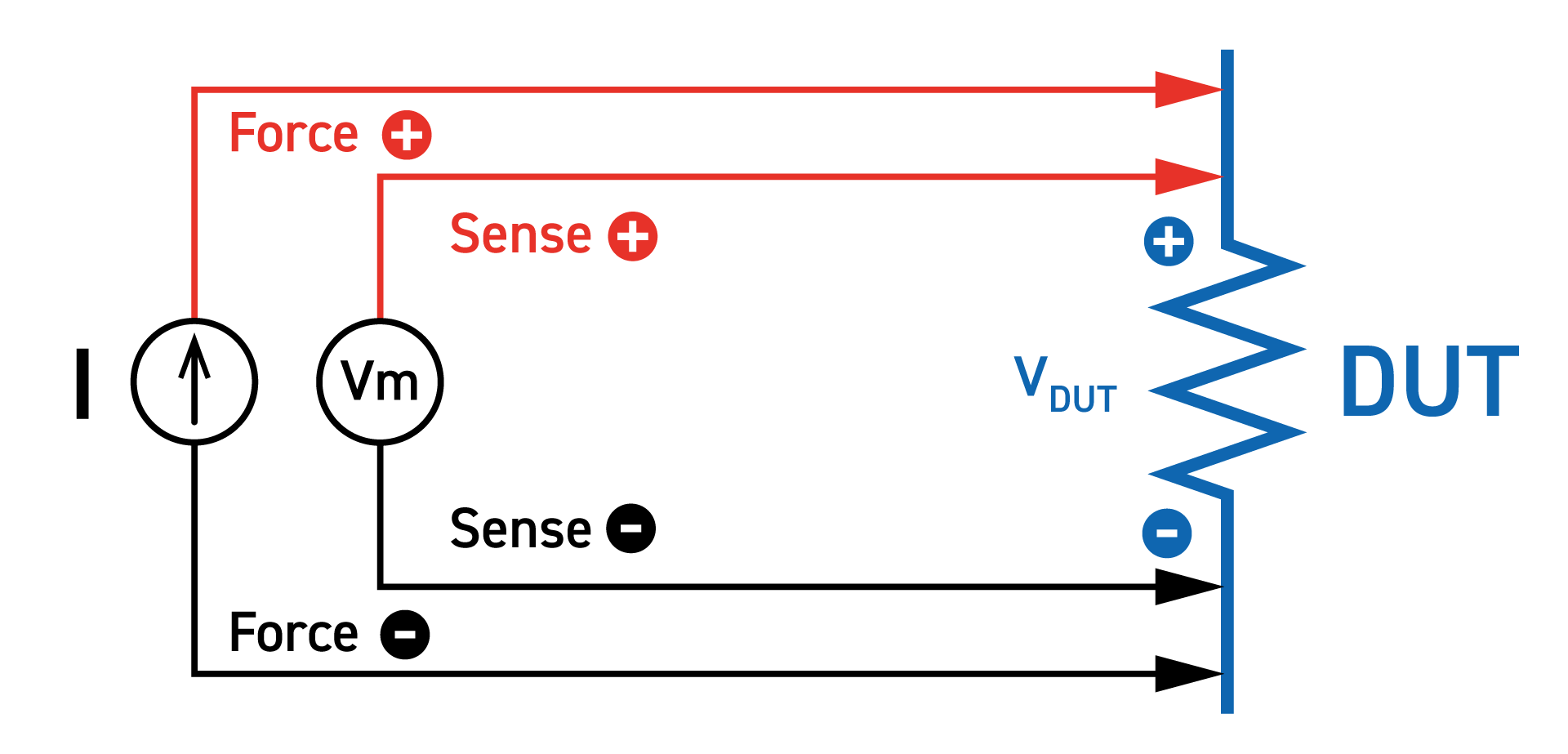

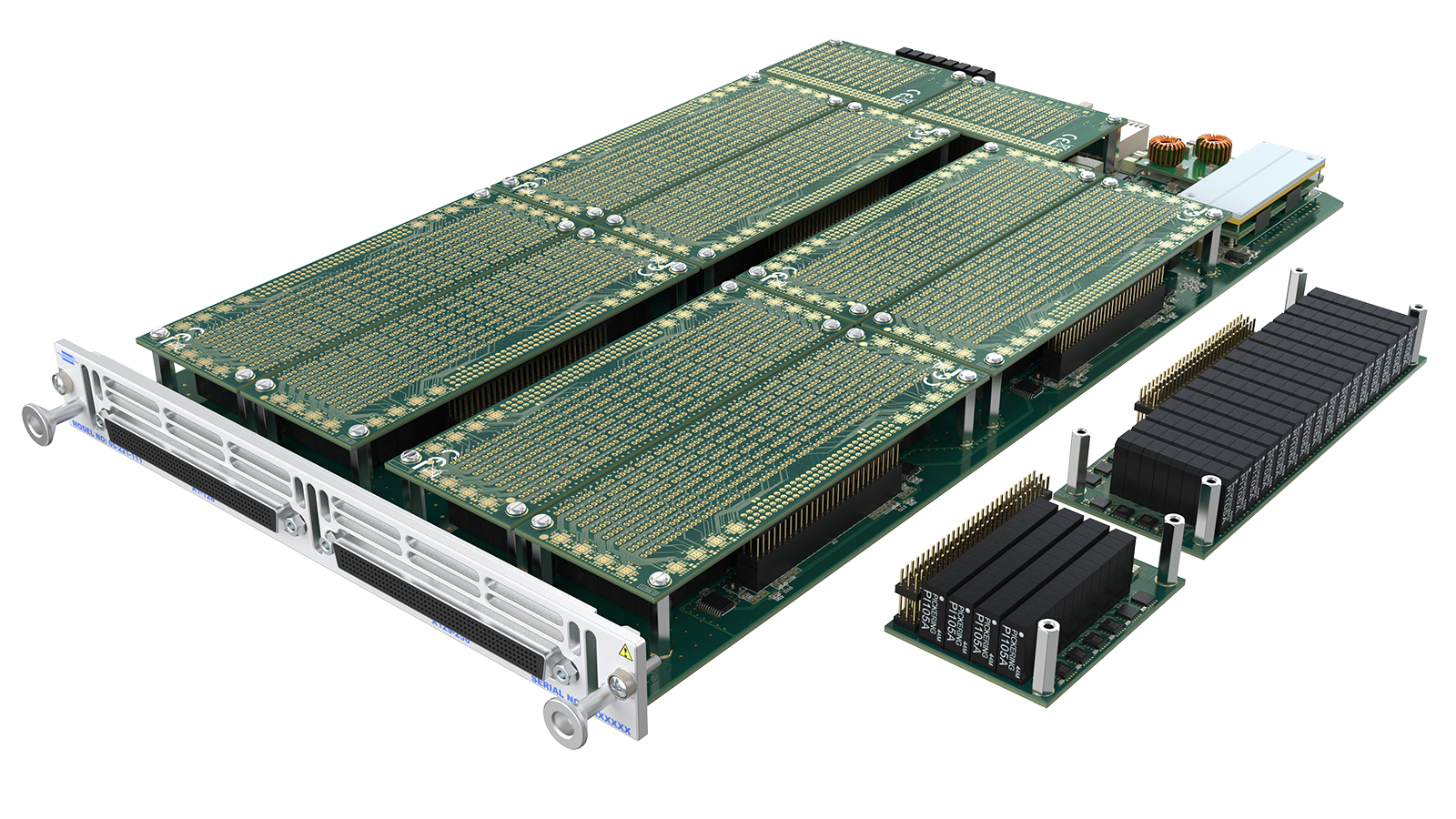

65-221は、図2に示すように、高密度でスケーラブルなマトリックス・ソリューションを提供するように設計された、プラグイン形式のモジュラー・スイッチング・システムです。

図2 LXI 2U スケーラブル・シャーシ(65-200-002)に6つの65-221プラグイン・マトリックス・モジュールを取り付けた状態

プラグイン・モジュールは、コンパクトな2Uサイズのラックマウント・シャーシであるスケーラブル・シャーシ (65-200-002)に、入れて利用できます。 スケーラブル・シャーシは、最大6つのプラグイン・マトリックス・モジュールを収容する事ができ、業界標準のLXI準拠し、イーサネットからの制御を可能とします。 。

プラグイン・モジュール65-221には、長寿命と優れた低レベル信号スイッチング性能を実現するピカリング社の計測グレードのリード リレーを使用したデュアル128×4サブ・マトリックスで構成され、最大で1Aおよび150 VDCまでの信号を扱う事ができます。ユーザーは、DUTに合わせて、必要なプラグイン・モジュールの数を指定し、必要に応じてシャーシを現場でアップグレードしてマトリックスのサイズを拡張できます。

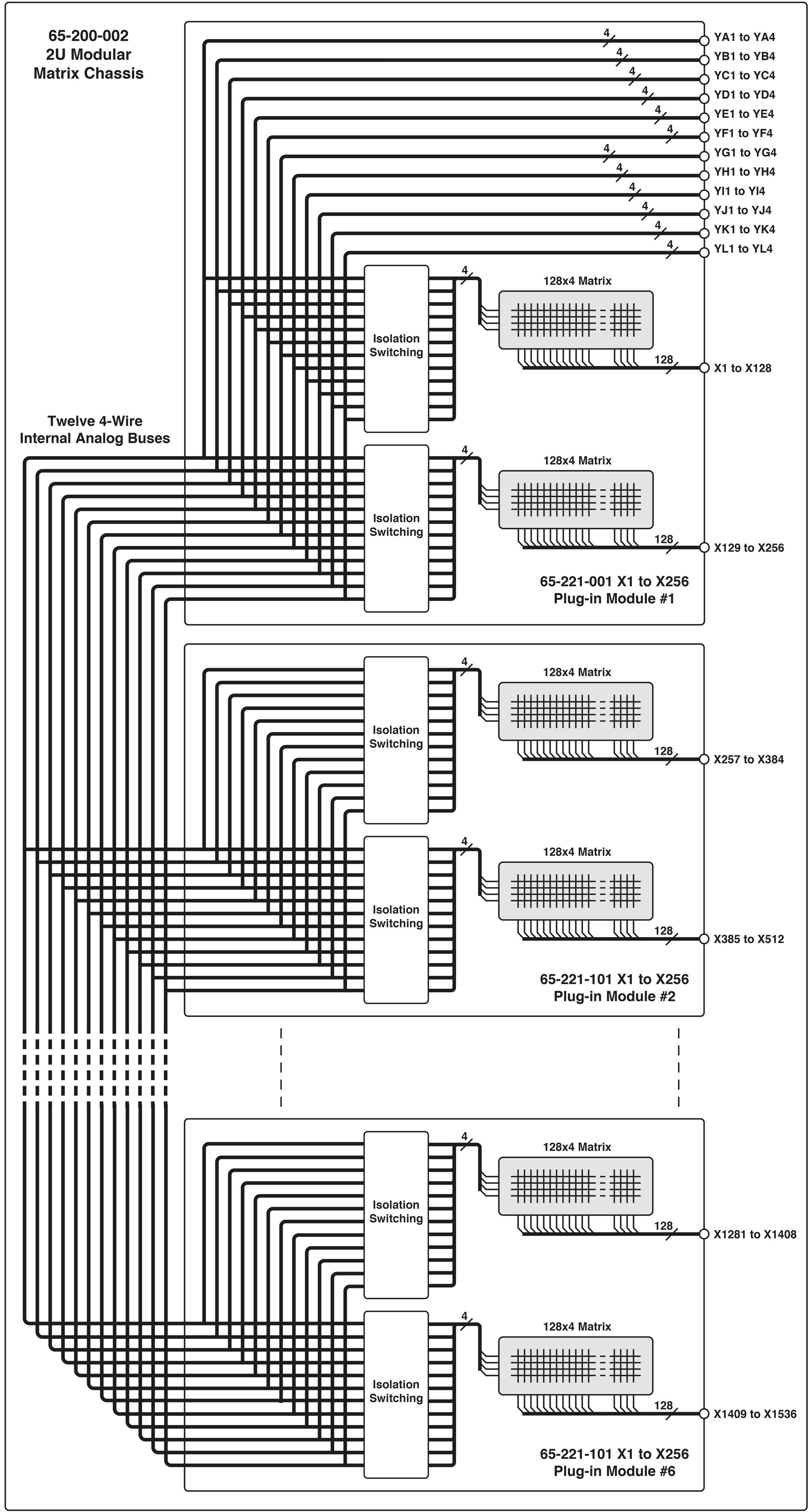

図3 65-221概要図

シャーシのバックプレーンは、プラグイン間で電源、制御信号、および12個のアナログ・バスを分配します。各バスは4つのレーンで構成され、図3に示すように、分離リレーを介して任意のプラグインの128×4サブ・マトリックスのYバスにルーティングできます。その結果、プラグインは、単一の1536×4マトリックスから12個の個別の128×4マトリックスまで、非常に柔軟なさまざまなスイッチング構成を形成できます。

大規模並列パラメトリック・テスト

12本の4線アナログ・バスにより、最大12個のSMUを同時に使用して、高度に並列化されたパラメトリック・テスト・アプリケーションを実現できます。各SMUからの 4つの接続はそれぞれ、アナログ・バスを介して6つのプラグイン・モジュールにわたる12個の個別の128×4サブ・マトリックスのいずれかのYバス ラインにルーティングでき、任意のDUTピンに接続できます。図4は、この具体的な例の1つを示しています。各SMUは個別のサブ・マトリックスに接続され、隣接するDUTピン間の抵抗を測定するために使用されます。

12個のSMUにより同時に4線式パラメトリック測定を行います。次に、各サブ・マトリックスのX接続が次の2つのDUTピンのセットに接続されます。このプロセスが繰り返され、SMUあたり最大32回の抵抗測定 (128個のサブ・マトリックスX接続を4で割った値) が行われます。つまり、6つのプラグイン全体で合計384回の測定が行われます。

図4. 並列パラメトリック・テスト用に、65-221を個別の12個の128x4のマトリックスとして構成

スキャン・リスト・シーケンスとトリガー

この測定ループの速度を最適化するために、65-221シャーシにはスキャン・リスト・ シーケンス・サービスが装備されています。これにより、すべての個別測定のスイッチ設定のシーケンスがシャーシ・コントローラ・ファームウェアにロードされ、マスター機器として指定されたSMUの1つからのハードウェア「準備完了(ready)」トリガーによってシーケンスが開始されます。必要なスイッチ設定が行われると、シャーシはマスターに「準備完了」トリガーを返します。マスターは次に、すべてのSMUにパラメトリック測定を実行してオンボード・メモリに記録するように要求します。マスターはすべての機器から「測定完了(measurement complete)」信号を受信すると、マトリックスに「準備完了」トリガーを送信します。マトリックスはスキャン・リストの次のスイッチ設定を実行し、プロセスを繰り返します。その後、保存されているすべてのSMU測定を分析できます。

スイッチ状態シーケンスはLXIコントローラ内に保存されるため、ホストCPUとイーサネット・トラフィックの負荷が大幅に軽減され、システム全体の遅延が短縮されます。

アプリケーションの柔軟性

DUTに1536を超えるテスト接続が必要な場合は、各ユニット間の12個の4線バスをデイジー・チェーン接続することで、複数の65-221マトリックス・システムを簡単に追加できます。ピカリング社のConnect部門では、標準またはカスタムのケーブル・アセンブリを提供しており、お客様の必要なケーブルを製造できます。これらの複雑なスイッチング・システムのプログラミングを簡素化するために、ピカリング社のSwitch Path Manager自動信号ルーティング・アプリケーションを使用して、必要な複数のリレー操作をCONNECT (SMU7_HI、DUT_274) などの単一のエンドポイント間のコマンドとして扱う事ができます。

アプリケーションに必要なSMUの数が少ない場合は、12個ではなく最大6個の SMUを搭載できる低コストの65-221プラグイン・バリアントを利用できます。 さまざまなDUTアプリケーションに対応するため、ピカリングは、Y軸信号とアナログ バスの数が異なる3つのマトリックス・プラグイン・バリアントを開発しました。 8本の信号幅を持つ6本のバス、16本の信号幅を持つ3本のバス、32本の信号幅を持つ1本のバス (それぞれモデル番号 65-223、-225、-227) で、すべて 65-221 と同じ65-200-002シャーシを使用します。

保守性

マトリックスに取り付けられたピカリング社のリード・リレーは、通常の動作条件下では極めて信頼性が高いものです。ただし、機械部品であるため機械的耐久性があり、最大動作仕様を超える信号を受けると故障する可能性があります。マトリックスはパラメトリック・テスト・システムの中心であるため、リレーの故障によるダウンタイムは信頼性テスト・プログラム全体に重大な影響を及ぼす可能性があります。65-221 は、この潜在的な問題に対処して平均修復時間 (MTTR) を最小限に抑えるように根本から設計されています。プラグイン・モジュールの各128×4 サブ・マトリックスは、図5に示すように、高信頼性ソケットを介してプラグインに接続する4つの32×4のドーター・ボードで構成されています。

図 5. 65-221のサブ・マトリックスは簡単に交換可能なドーター・ボード構造です

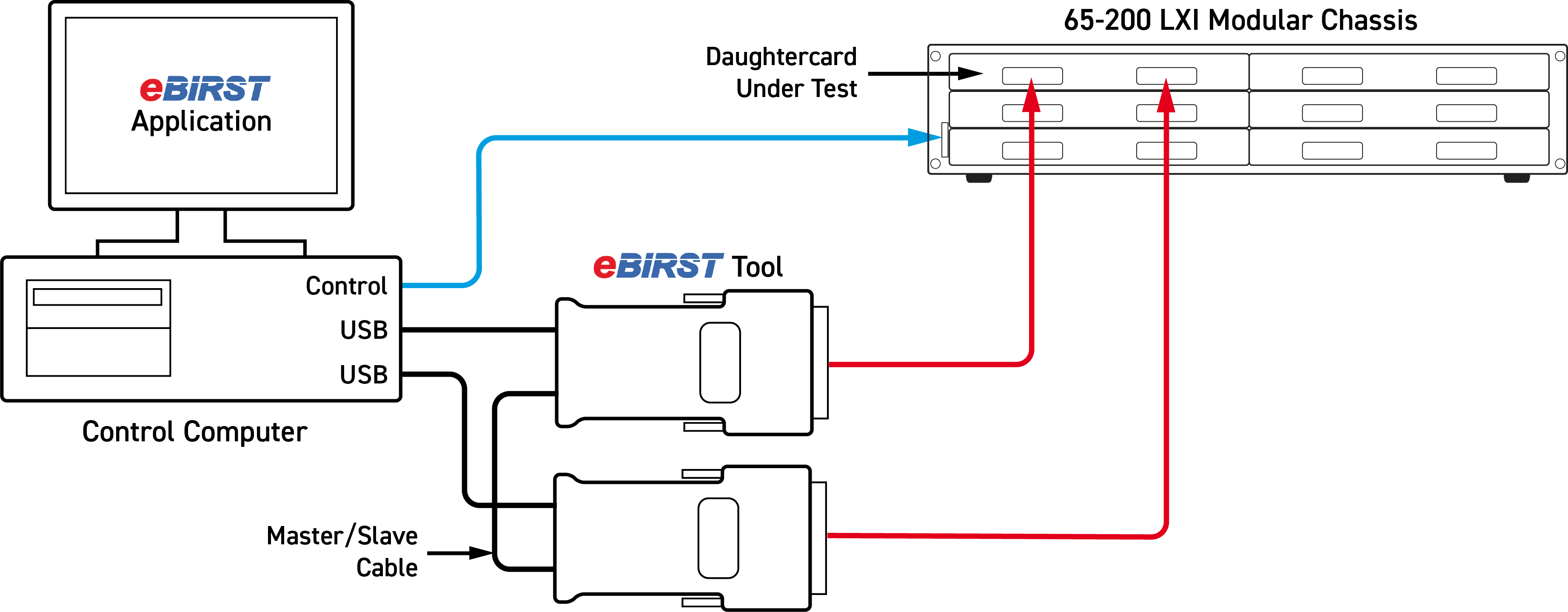

アナログ・バスを各サブ・マトリックスに接続する分離リレーも同様のドーター・ボードの形式で実装されています。リレーの故障が疑われる場合、ピカリング社では故障したリレーをユーザー自身の手で、見つけるために使用できる2つの診断テスト・ツールを提供しています。65-221には、特定のプラグインの故障を診断できる統合BIRST (Built-In Relay Self-Test)ツールがあり、多くの場合、個々のドーター・ボード故障まで診断できます。スペアが保管されている場合は、故障したモジュールを既知の正常なスペアと交換できます。その後、マトリックスを再度組み立て、再テストし、すぐにサービスに戻すことができます。定期メンテナンスを行う場合には、故障したドーター・ボードをシャーシに再度取り付けし、ピカリング社のeBIRSTアプリケーションでテストする事ができます。これは、各プラグイン間に接続された2つの外部USB制御テスト・ツールを使用する事で、すべてのリレーの機能を迅速かつ正確にテストします (図6を参照)。プラグイン・モジュールには、交換用のスペア・リレーが用意されており、リレーはスルー・ホール実装のため、eBIRSTアプリケーションにより、故障が指摘されたリレーはユーザー自身の手で、簡単に取り外して交換する事ができます。 修理した、ドーター・ボードを再度テストし、再使用するために、再度スペアとする事ができます。

図6 eBIRST 診断テスト・ツール・システムを使用し65-221 LXI スイッチ・ユニットをテストできます

まとめ

パラメトリック・テストは半導体デバイスの信頼性テストに不可欠ですが、ピン数の多いデバイスでは時間のかかるプロセスになることがあります。半導体メーカーが新製品設計の市場投入までの時間を短縮できるように、ピカリング社では、大規模な並列パラメトリック・テストを容易にし、デバイスの検証サイクル時間を大幅に短縮できる、高速で

MTTRの低い柔軟なスイッチ・マトリックス・プラットフォームを開発しました。

お問合せ